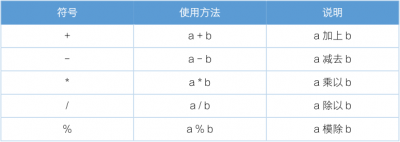

首先我们介绍的是算术运算符,所谓算术逻辑运算符就是我们常说的加、减、乘、除等,这类运算符的抽象层级较高,从数字逻辑电路实现上来看,它们都是基于与、或、非等基础门逻辑组合实现的,如下。

/是除法运算,在做整数除时向零方向舍去小数部分。

%是取模运算,只可用于整数运算,而其他操作符既可用于整数运算,也可用于实数运算。

例子:我们在生成时钟的时候,必须需选择合适的timescale和precision。当我们使用“PERIOD/2”计算延迟的时候,必须保证除法不会舍弃小数部分,所以实际上我们应该使用实数除法“PERIOD/2.0”。

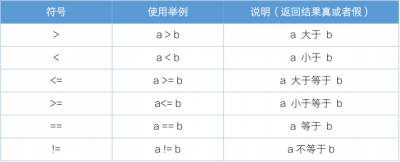

关系运算符

关系运算符主要是用来做一些条件判断用的,在进行关系运算符时,如果声明的关系是假的,则返回值是 0,如果声明的关系是真的,则返回值是 1;所有的关系运算符有着相同的优先级别,关系运算符的优先级别低于算术运算符的优先级别。如下。

逻辑运算符是连接多个关系表达式用的,可实现更加复杂的判断,一般不单独使用,都需要配合具体语句来实现完整的意思,如下。

Verilog 语言为了让连续赋值的功能更加完善,于是又从 C 语言中引入了条件操作符来构建从两个输入中选择一个作为输出的条件选择结构,功能等同于 always 中的 if-else 语句,如下。

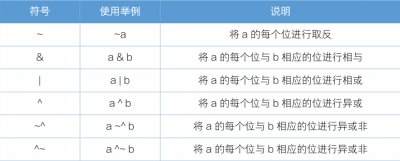

位运算符是一类最基本的运算符,可以认为它们直接对应数字逻辑中的与、或、非门等逻辑门。

位运算符的与、或、非与逻辑运算符逻辑与、逻辑或、逻辑非,虽然它们处理的数据类型不一样,但是从硬件实现角度上来说,它们没有区别的,如下。

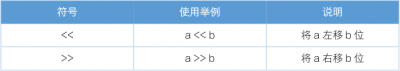

在 Verilog 中有两种移位运算符:左移位运算符和右移位运算符,这两种移位运算符都用 0来填补移出的空位。如下。

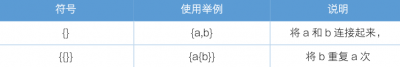

在 Verilog 中有一个特殊的运算符,就是我们的位拼接运算符。用这个运算符可以把两个或多个信号的某些位拼接起来进行运算操作。如下。

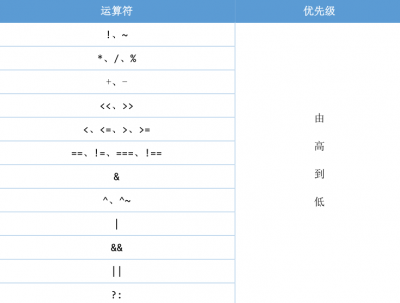

运算符一多,必然涉及到优先级的问题,为了便于大家查看这些运算符的优先级,我们将它们制作成了表格,如下。